# Aula 6: Transistores de Potência - MOSFET

Prof. Allan Fagner Cupertino afcupertino@ieee.org

#### Sumário

☐ Estrutura interna;

☐ Física de operação do MOSFET;

☐ Características de comutação;

☐ Avanços e estruturas melhoradas.

# Estrutura Interna

#### História e curiosidades

- Primeira ideias em torno dos anos 40 (Ideia abandonada, devido ao fracasso nos experimentos);

- 1954: Transistor bipolar de junção;

- 1959: Primeiro MOSFET por Atalla e Kahng (Bell);

- ☐ 1969: VMOS pela Hitachi e DMOS pelo ETL;

- 1974: Amplificadores de áudio;

- ☐ 1978: Hex-FET de Potência comercializado pela International Rectifier.

- ☐ 1978: Superjunction MOSFET Osaka University.

Fonte: <a href="https://www.littelfuse.com/products/power-semiconductors/discrete-mosfets.aspx">https://www.littelfuse.com/products/power-semiconductors/discrete-mosfets.aspx</a>

#### História e curiosidades

- ☐ 1962: primeiro MOS IC planar;

- ☐ 1963: CMOS(Complementary MOS);

- Desenvolvimento dos computadores.

## Tipos de MOSFETs

- ☐ MOSFET tipo depleção:

- Canal físico;

- Versões tipo N e P;

- Necessita de uma tensão negativa para desligar;

- MOSFET tipo intensificação;

- Canal é formado pelo efeito de campo;

- Versões tipo N e P;

- Não necessita de tensão negativa;

- Mais popular em EP.

Fonte: M. H. Rashid: Eletrônica de Potência: Dispositivos, circuitos e aplicações. 4ª. Edição, Pearson, 2014 (Livro texto)

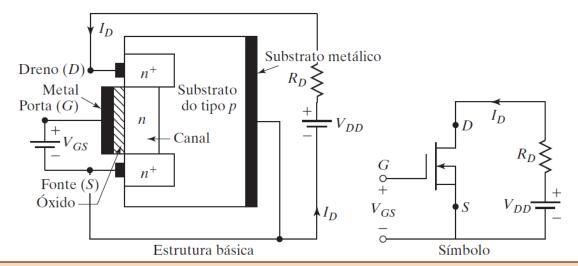

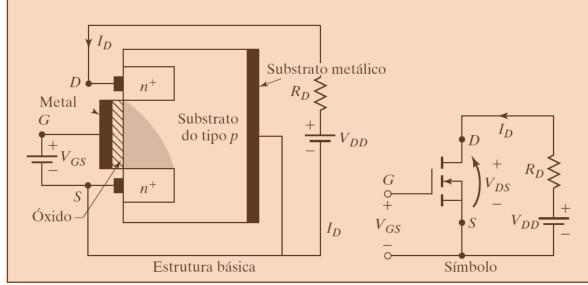

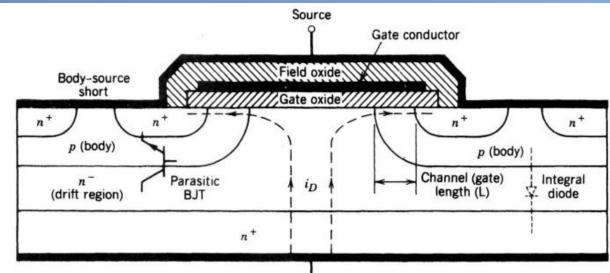

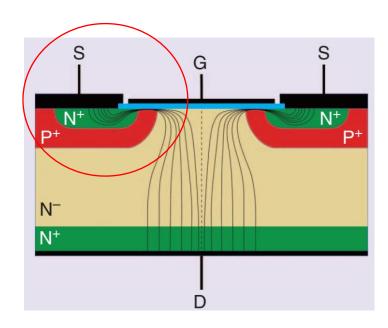

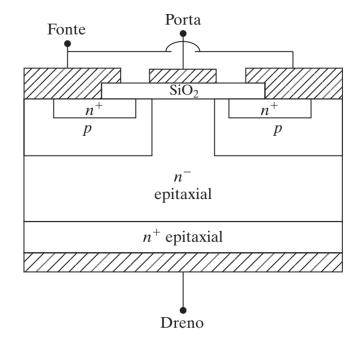

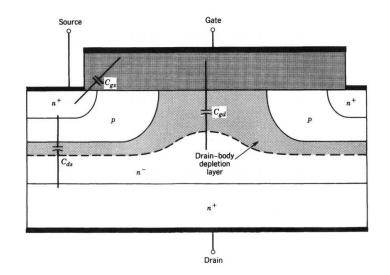

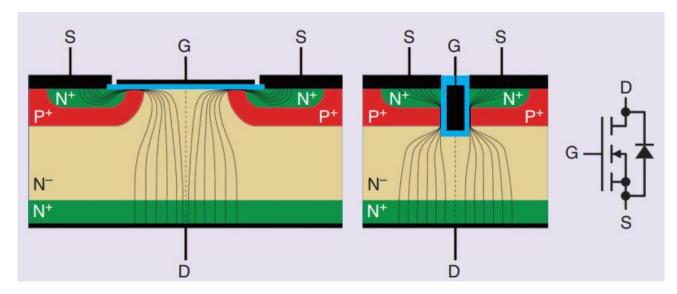

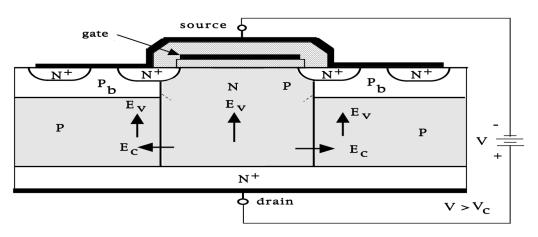

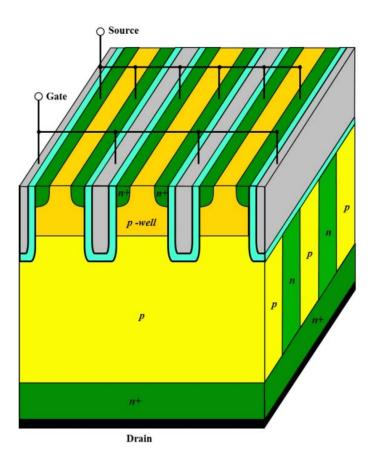

#### MOSFET de Potência

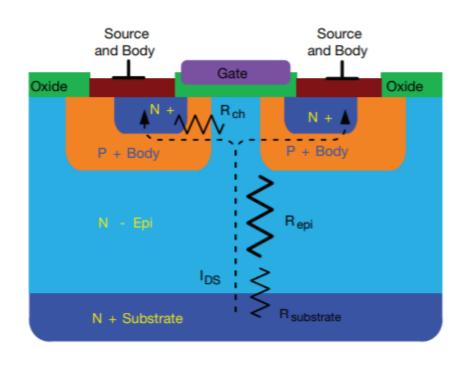

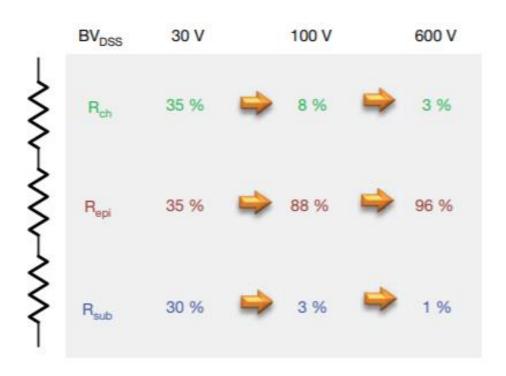

- ☐ Estrutura vertical (VDMOS)

- Vertical Difused MOS

- Maior área de condução de corrente;

- Reduz a resistência série equivalente.

Fonte: M. H. Rashid: Eletrônica de Potência: Dispositivos, circuitos e aplicações. 4ª. Edição, Pearson, 2014 (Livro texto)

Porta

Dreno

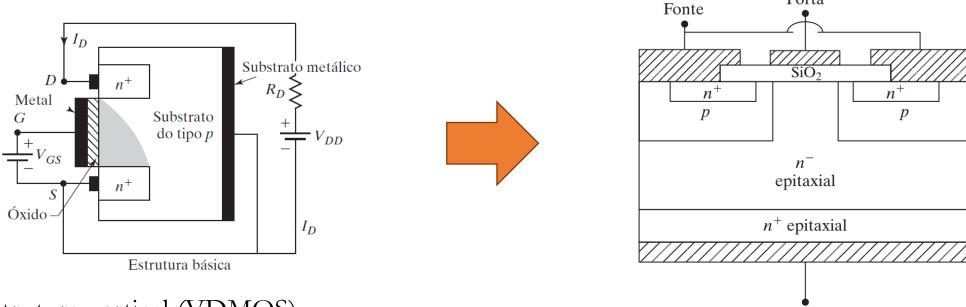

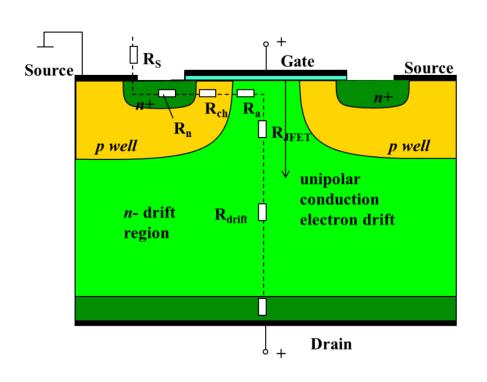

#### Estrutura detalhada - VDMOS

- ☐ Concentrações de dopagem típicas:

- $\rightarrow n^+ \rightarrow \text{aproximadamente } 10^{19} \text{ cm}^{-3};$

- $> p^+ \rightarrow \text{aproximadamente } 10^{16} \text{ cm}^{-3};$

- $n^- \to \text{entre } 10^{14} 10^{15} \text{ cm}^{-3};$

- ightharpoonup região  $n^- oup$  define a tensão de ruptura;

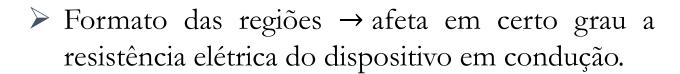

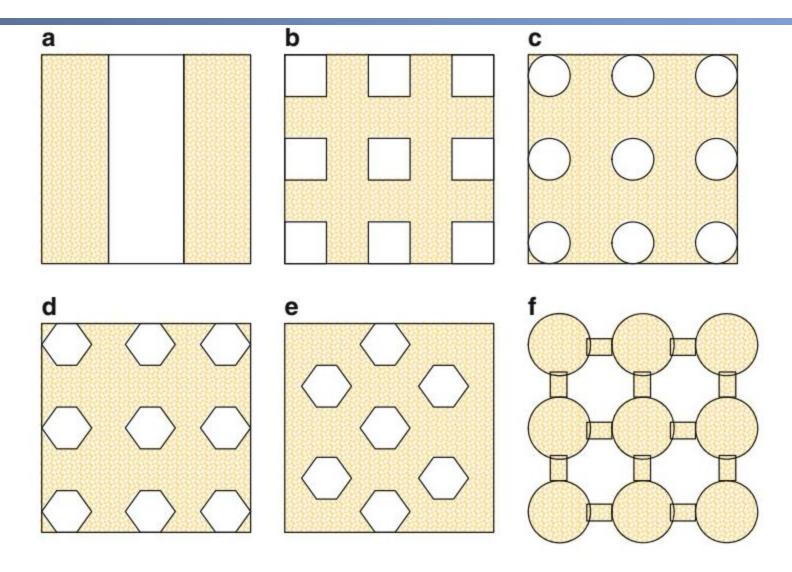

### Exemplo – HEXFET

□ HEXFET: Marca de uma estrutura desenvolvida pela International Rectifier → regiões hexagonais.

Fonte: International Rectifier. Application Note NA-937.

## Pontos importantes - MOSFET

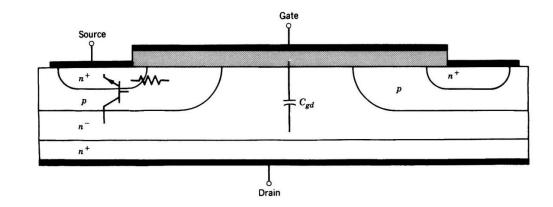

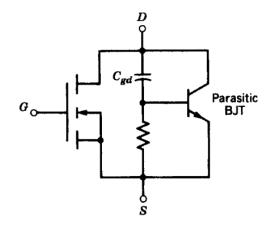

- ☐ Transistor NPN parasita

- Curto circuito do corpo com a fonte.

- ☐ Diodo anti-paralelo intrínseco

- > Parte do transistor NPN.

- ☐ Óxido da porta: espessura em torno de 100 nm;

- $\square$  Região  $n^-$ : Define a tensão de bloqueio do dispositivo

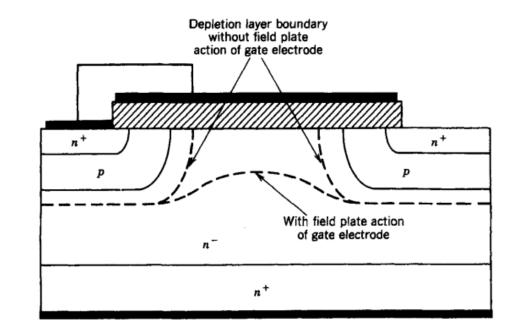

- Extensão da metalização da porta

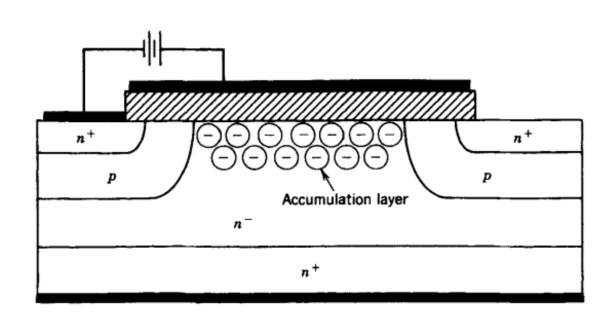

- $\triangleright$  Camada de acumulação: melhora a condutividade da região  $n^-$ ;

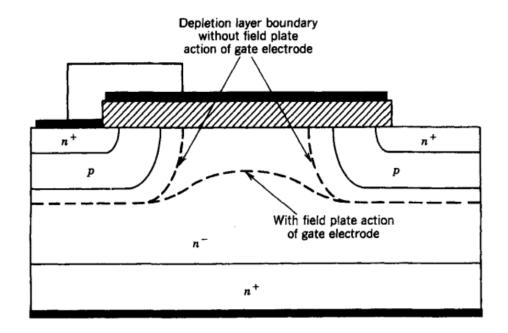

- Funciona como uma equipotencial, diminuindo o raio de curvatura da região de depleção.

Fonte: Mohan, Undeland and Robbins: Power Electronics: Converters, Applications and Design. 3rd. Edition, John Wiley, 2003.

Drain

### Extensão da metalização da porta

☐ Condução: Acumulação

☐ Bloqueio: Equipotencial

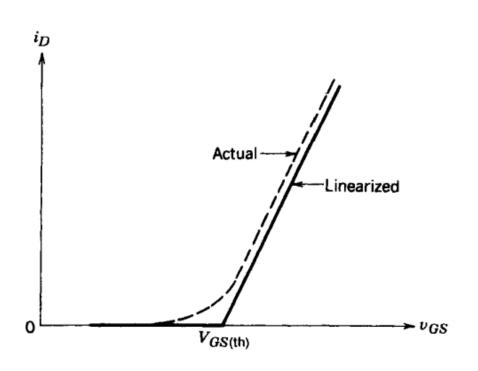

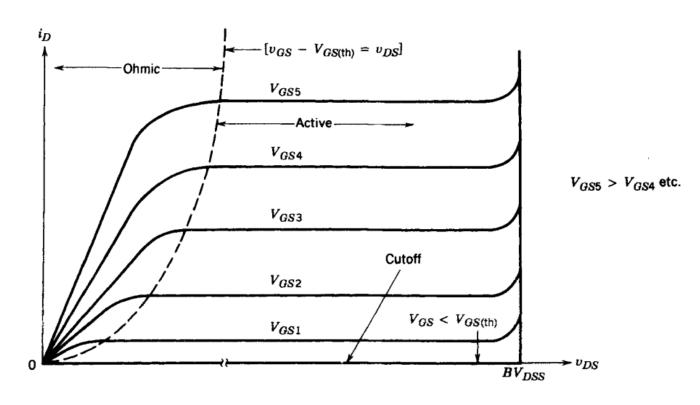

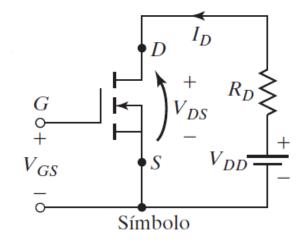

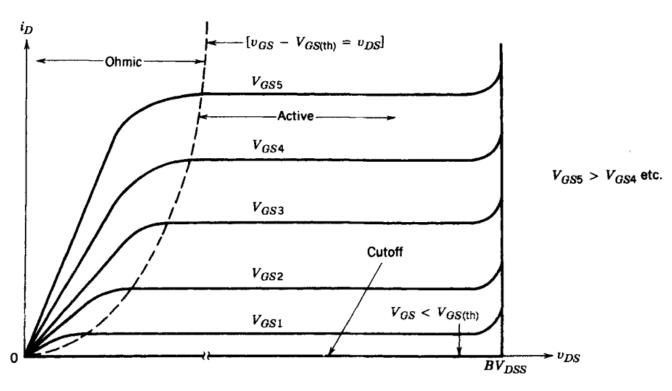

#### Curva I x V de um MOSFET

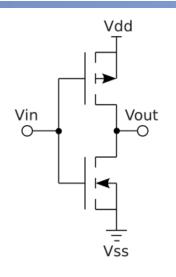

# Física de operação

### Característica I – V: TBJ convencional

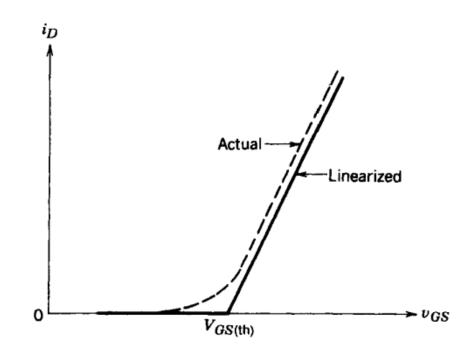

□ Transcondutância → relação entre a corrente de dreno e a tensão porta-fonte;

■ MOSFET: dois diodos em anti-paralelo;

☐ Princípio de condução baseado na aplicação de tensão entre porta (G) e fonte (S);

$\square$  Tensão limiar  $v_{GS(th)}$  (threshold voltage): Tensão mínima para garantir condução de corrente;

Fonte: F. Iannuzzo, C. Abbate and G. Busatto, "Instabilities in Silicon Power Devices: A Review of Failure Mechanisms in Modern Power Devices," in IEEE Industrial Electronics Magazine, vol. 8, no. 3, pp. 28-39, Sept. 2014, doi: 10.1109/MIE.2014.2305758.

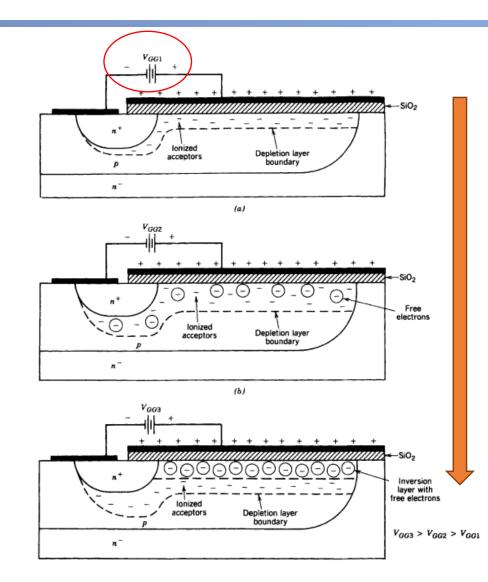

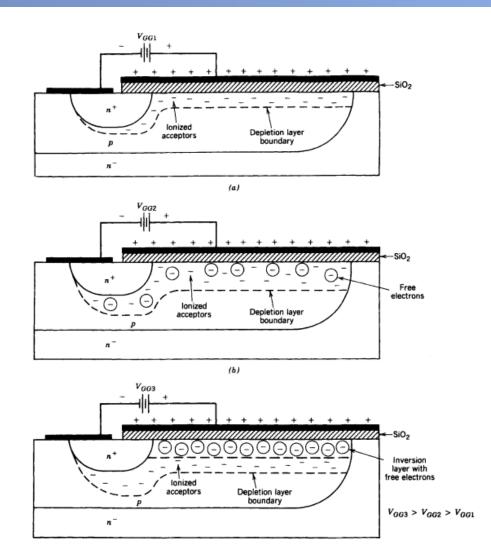

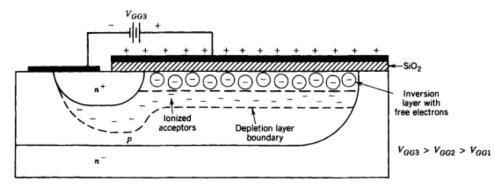

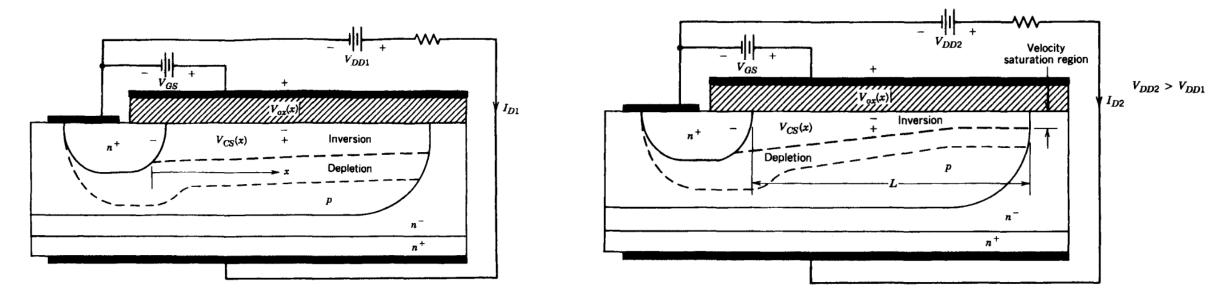

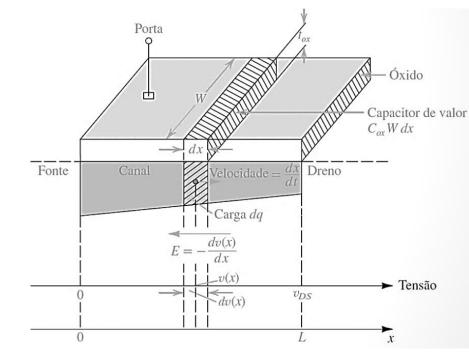

## Efeito de Campo

- Estrutura da porta similar a um capacitor;

- ☐ Campo elétrico atrai elétron e repele as lacunas do material tipo p;

- Elétrons são gerados por ionização térmica são atraídos e lacunas repelidas;

- $\square$  Aumento de  $v_{GS}$  resulta em um aumento de espessura da camada de depleção;

- ☐ Isto faz com que uma parcela da região p comece a comportar como uma região n;

## Efeito de Campo

- ☐ Formação do canal (ou camada de inversão).

- A tensão limiar  $v_{GS(th)}$  relaciona-se ao ponto em que a concentração de elétrons na região de depleção se torna próxima a concentração de dopagens;

- ☐ Efeito de campo: Mudança de condutividade de um material semicondutor por ação de um campo elétrico;

- $\square$  Se  $v_{GS} > v_{GS(th)}$  a camada de inversão torna-se mais largo e mais condutivo!

#### Tensão de limiar

- ☐ Tipicamente varia de 2 a 5 Volts em MOSFETs de potência;

- ☐ Dependente de diversos fatores:

- > Tipo de condutor;

- > Impurezas inseridas no óxido;

- $\triangleright$  Concentração de dopagem da camada  $p^+$ ;

- Capacitância do óxido por unidade de área:

$$C_{ox} = \frac{\epsilon_{ox}}{t_{ox}}$$

onde  $\epsilon_{ox}$  é a constante dielétrica do óxido e  $t_{ox}$  é a espessura do óxido;

$\square$  Ajuste fino: impurezas na região  $p^+$  próximo ao óxido.

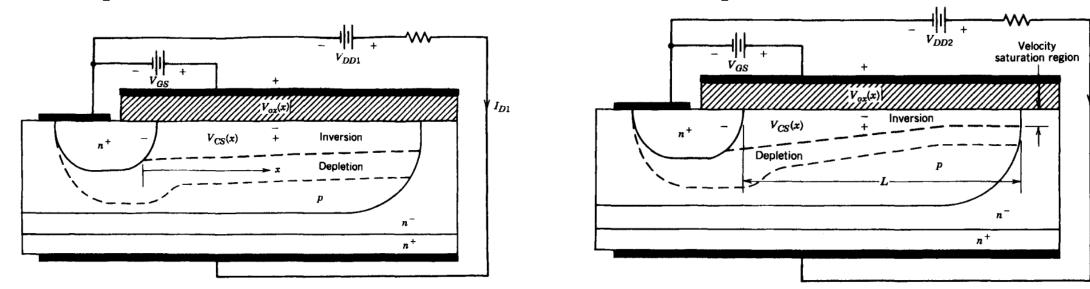

# Controle da corrente de dreno pela tensão $v_{GS}$

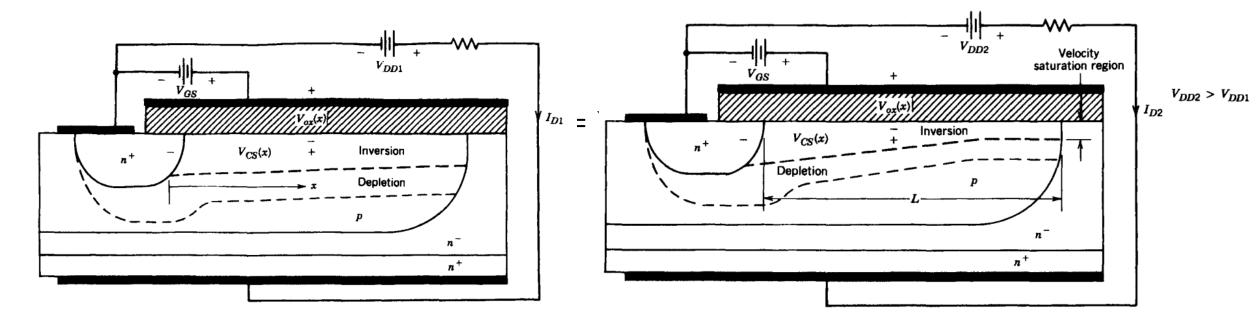

- Ao aplicar uma tensão entre dreno e fonte haverá uma circulação de corrente;

- $\square$  Neste caso os elétrons serão acelerados pelo campo elétrico gerado por  $V_{DD}$ ;

- Um aumento incremental de  $V_{DD}$  resulta em um aumento de  $I_D$ ;

- O MOSFET opera na região ôhmica;

- Note que a camada de inversão é aproximadamente uniforme.

Fonte: M. H. Rashid: Eletrônica de Potência: Dispositivos, circuitos e aplicações. 4ª. Edição, Pearson, 2014 (Livro texto)

Fonte: Mohan, Undeland and Robbins: Power Electronics: Converters, Applications and Design. 3rd. Edition, John Wiley, 2003.

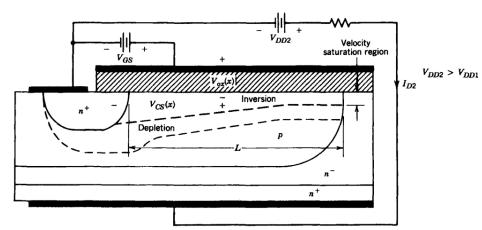

# Estreitamento da região de inversão (Pinch-off)

- $\square$  Quando  $I_D$  aumenta,  $v_{CS}(x) = R_{CS}(x)I_D$  aumenta e portanto,  $v_{ox}(x)$  reduz;

- $\square v_{CS}(x=L)=v_{DD};$

- ☐ Campo não é uniforme → estreitamento da região de inversão.

## Curvatura da região ôhmica

- A redução da largura do canal leva a um aumento da resistência elétrica equivalente;

- ☐ Isto ocasiona uma curvatura da região linear.

# E agora José?

- $\square$  Questão: E se  $I_D$  é tal que  $v_{GS} v_{DS} = V_{GS(th)}$ ?

- Este raciocínio leva a concluir que a camada de inversão deixaria de existir e nenhuma corrente seria capaz de fluir pelo MOSFET;

- ☐ Na prática, isto não ocorre! A vida real é bem mais complicada.

Fonte: Mohan, Undeland and Robbins: Power Electronics: Converters, Applications and Design. 3rd. Edition, John Wiley, 2003.

$V_{DD2} > V_{DD1}$

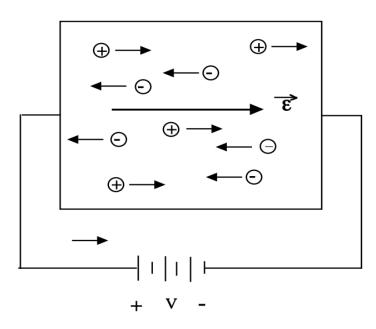

#### Corrente de deriva

- Princípio de conservação da carga: A corrente é a mesma no canal;

- ☐ Isso quer dizer que quanto mais estreita a região, maior a densidade de corrente;

- $\square J_D = q\mu_n nE \rightarrow$  maior campo elétrico no final da camada de inversão.

### Velocidade dos portadores versus E

Fonte: Mohan, Undeland and Robbins: Power Electronics: Converters, Applications and Design. 3nd. Edition, John Wiley, 2003.

$$v_D = \mu E$$

Fonte: Baliga, B. J. "Fundamentals of Semiconductor Devices", Springer.

#### Efeito resultante

- ☐ Este campo elétrico maior apresenta dois resultados:

- > O campo elétrico elevado vai ajudar a manter o canal com uma espessura mínima;

- A velocidade de arraste irá atingir o valor de saturação (mobilidade varia com campo elétrico e densidade de portadores);

- $\square$  No ponto que a velocidade satura,  $v_{GS} v_{DS} = v_{GS(th)}$  e o dispositivo entra na região ativa.

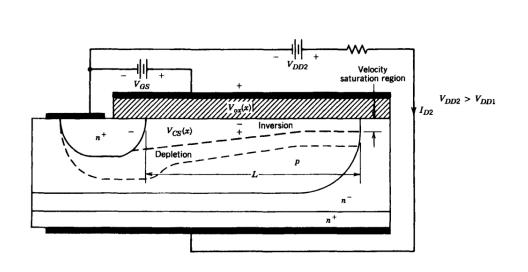

## Região ativa

- $\square$  Um aumento da tensão  $v_{DD}$  leva a um ligeiro aumento do comprimento da região de espessura mínima;

- ☐ Atinge-se a região ativa.

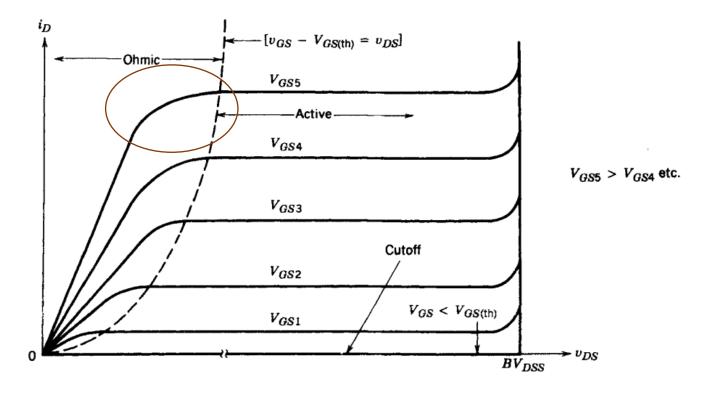

# Região ativa

$\square$  Note que quanto maior  $v_{GS}$ , maior a largura do canal;

Além disso, maior o valor de corrente capaz de causar a saturação de velocidade;

☐ É possível mostrar que na região ativa:

Onde

$$i_D = K \left( v_{GS} - v_{GS(th)} \right)^2$$

$$K = \frac{\mu_n C_{ox} W}{2L}$$

Fonte: Boylestad, R. L. e Nashelsky, L.. Dispositivos Eletrônicos e Teroria de Circuitos.

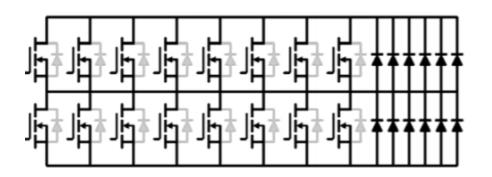

# Princípio de elevado ganho

$\square$  Para obter um elevado ganho,  $W \gg L$ ;

$\square$  Isto é obtido mantendo L o menor possível (limitado pela tensão de ruptura);

$\square$  A razão típica  $\frac{W}{L}$  é em torno de  $10^5$ ;

☐ Ela é obtida pela utilização de milhares de pequenos contatos de fonte;

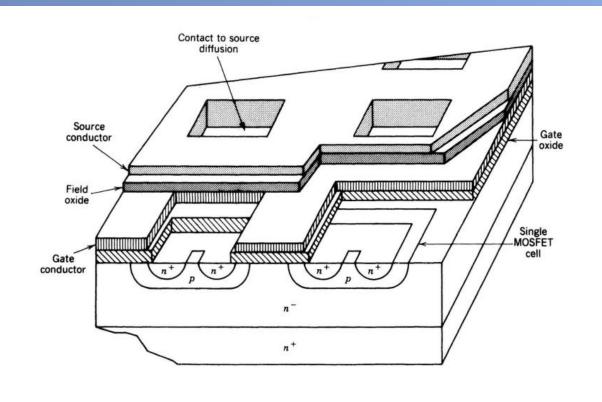

#### Diferentes estruturas de VDMOS

Fonte: Baliga, B. J. "Fundamentals of Semiconductor Devices", Springer.

# Comportamento de entrada

☐ É importante notar que o aumento quadrático é limitado a uma faixa;

$$i_D = K \left( v_{GS} - v_{GS(th)} \right)^2$$

☐ Isto ocorre porque a mobilidade cai devido a saturação de velocidade e a elevada densidade de carga;

$\square$  Isto leva a uma relação aproximadamente linear entre  $i_D$  e  $v_{GS}$ .

### Obrigado pela Atenção

www.gesep.ufv.br

https://www.facebook.com/gesep

https://www.instagram.com/gesep\_vicosa/

https://www.youtube.com/channel/UCe9KOSGORXh hDBIcxMU2Nw

https://play.google.com/store/apps/details?id=br.developer.gesep.estimate

# Características de comutação

# Introdução

Os MOSFETs são essencialmente mais rápidos que os transistores bipolares;

☐ Isto acontece porque o princípio de operação não necessita de excesso de portadores minoritários;

☐ A única movimentação de carga está associada as capacitâncias parasitas do dispositivo;

Fonte: M. H. Rashid: Eletrônica de Potência: Dispositivos, circuitos e aplicações. 4ª. Edição, Pearson, 2014 (Livro texto)

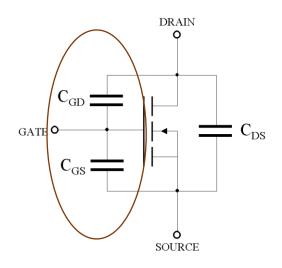

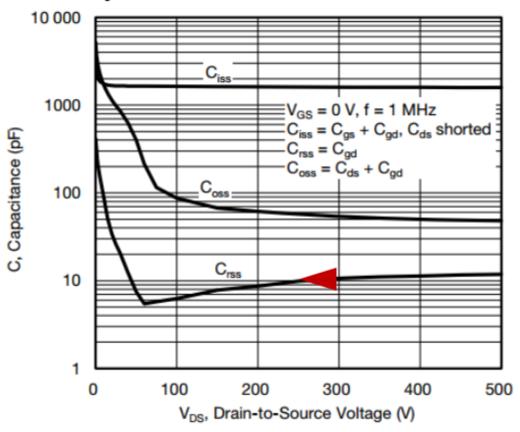

## Capacitâncias parasitas de um MOSFET

☐ Capacitâncias não são constantes (variam com a tensão aplicada);

$\square$   $C_{DS}$  é importante para o projeto de Snubbers;

$\square$   $C_{GD}$  e  $C_{GS}$  são importantes para o projeto do gate driver.

Fonte: Mohan, Undeland and Robbins: Power Electronics: Converters, Applications and Design. 3rd. Edition, John Wiley, 2003.

K. Shenai, C. Cavallaro, S. Musumeci and R. Pagano, "Modeling low-voltage power MOSFETs as synchronous rectifiers in buck converter applications," 38th IAS Annual Meeting., 2003

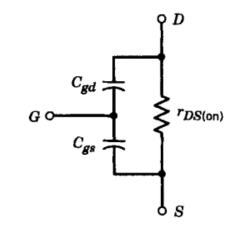

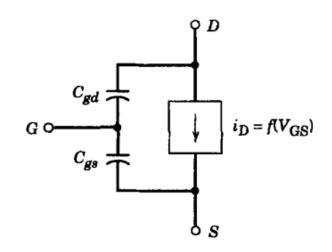

# Modelos de um MOSFET – Análise de comutação

☐ Região ôhmica → resistência elétrica;

$\square$  Região ativa e corte  $\rightarrow$  fonte de corrente controlada por  $v_{GS}$ ;

# Não-linearidade nas capacitâncias

- $\square$  As capacitâncias  $\mathcal{C}_{gs}$  e  $\mathcal{C}_{gd}$  não são constantes, mas variam com a tensão;

- ☐ Capacitâncias de Miller;

- $\square$   $C_{gs}$ : capacitância do óxido em série com a capacitância da região de depleção da interface Si  $SiO_2$ ;

- $\square$  Mudanças em  $C_{gd}$  de 10 a 100 vezes são tipicamente encontradas;

- $\square$  Aproximação que facilita a análise:  $C_{gd1}$  e  $C_{gd2}$

$C_{gd}$   $C_{gd2}$   $C_{gd1}$   $C_{gd1}$   $C_{gd1}$

$v_{GS} = v_{DS}$

Drain-body

Fonte: Mohan, Undeland and Robbins: Power Electronics: Converters, Applications and Design. 3rd. Edition, John Wiley, 2003.

200

# Variação da capacitância de um MOSFET

#### Vishay Siliconix SiHB20N50E MOSFET

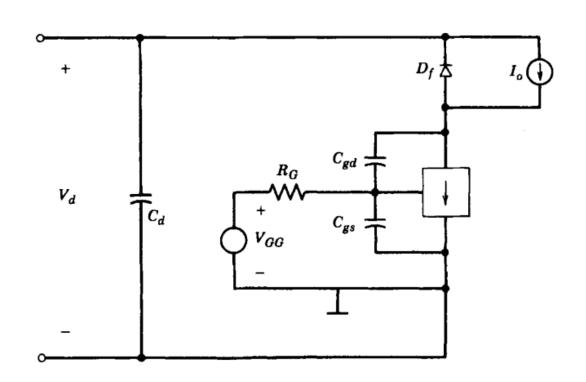

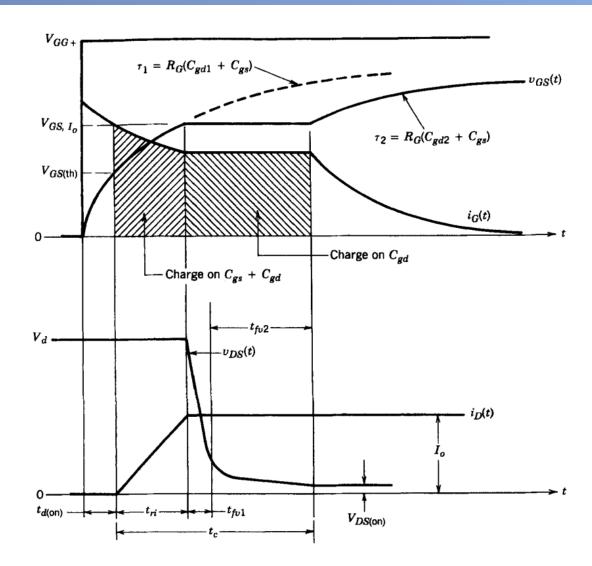

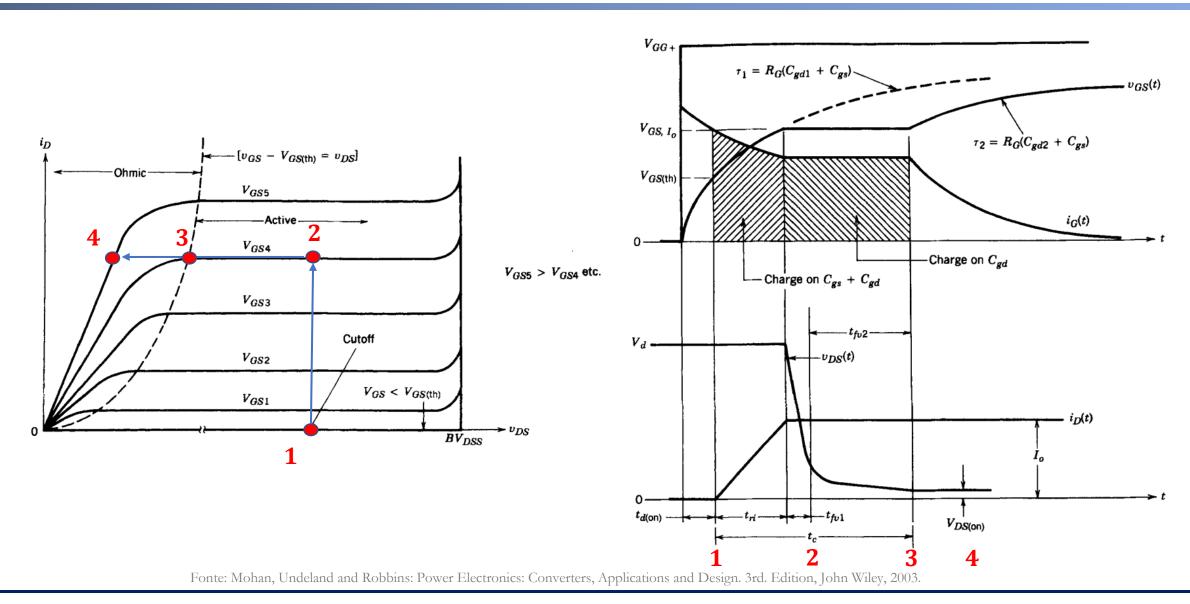

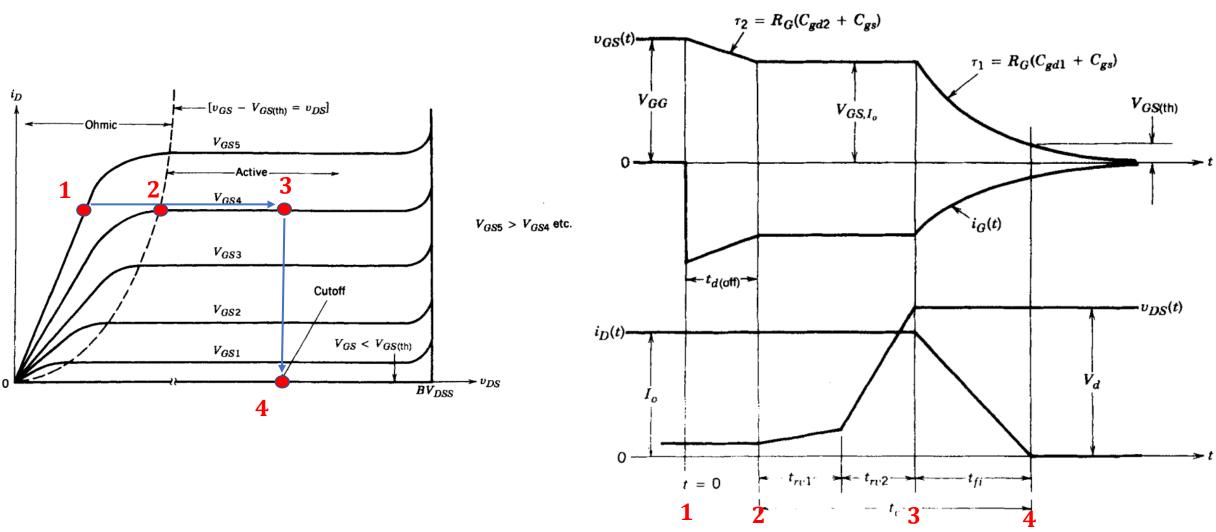

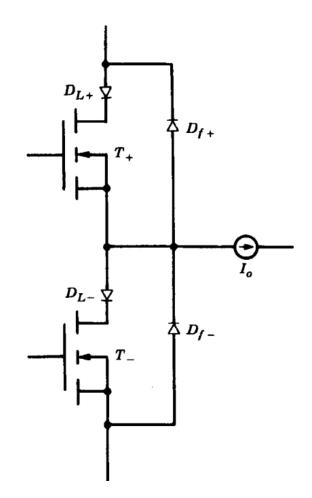

### Transitórios de comutação

■ Mesmo circuito utilizado para avaliar o TBJ de potência;

□ Note a presença de uma resistência de gate;

☐ Afeta diretamente a performance do dispositivo;

$\square$  Diodo  $D_f$  de roda livre para assumir a corrente  $I_o$  durante o <u>turn-off</u>

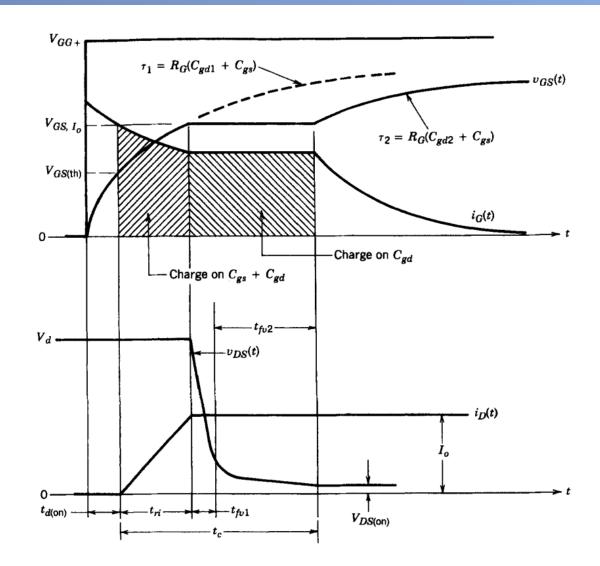

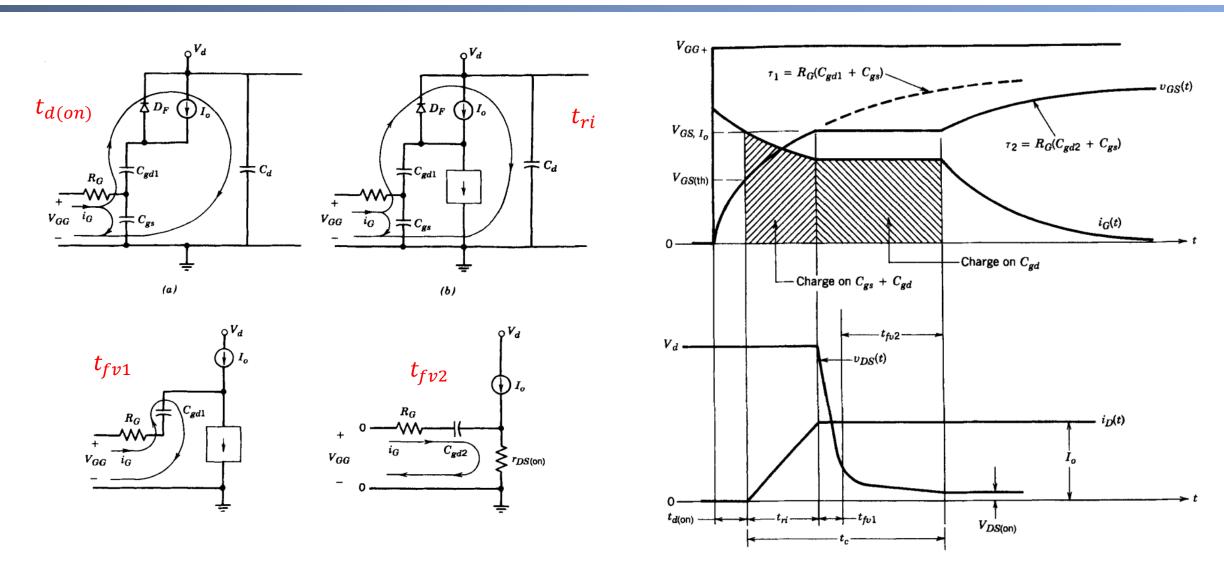

- $\square$  Crescimento da tensão  $v_{GS}$  até a tensão limiar;

- Aumento linear da corrente na região ativa;

- $\square$  Tensão em  $V_d$  pois o diodo ainda conduz;

- $\square$  Platô de Miller: Tensão de  $V_{GS} = V_{GS,I_o}$  (região ativa);

- $\square$  Tensão  $v_{DS}$  reduz. A mudança de derivada é relacionada a variação de  $\mathcal{C}_{gd}$  com a tensão;

$$\frac{dv_{DG}}{dt} = \frac{dv_{DS}}{dt} = \frac{i_G}{C_{gd}} = \frac{V_{GG} - V_{GS, I_o}}{R_G C_{gd}}$$

☐ A região ôhmica é atingida;

$\square$  A tensão  $v_{GS}$  aumenta atingindo o valor de regime permanente;

$\square$  O tempo de subida é mais lento pois  $C_{gd2} > C_{gd1};$

$\square$  O dispositivo atinge a tensão  $v_{DS(on)}$ .

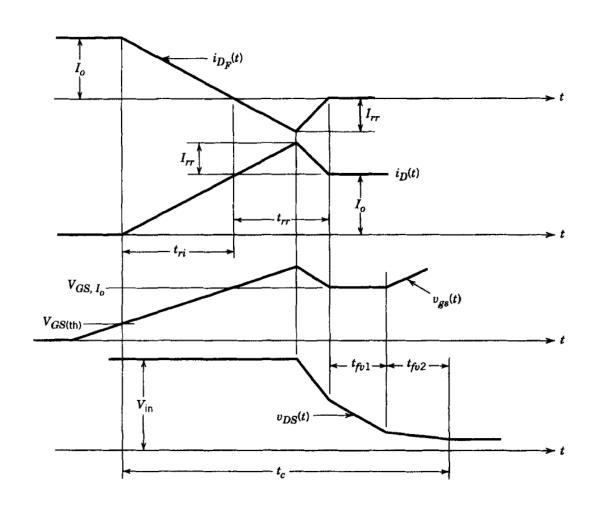

#### Efeito do diodo

- $\square$  Recuperação reversa:  $V_{GS} > V_{GS,I_o}$ ;

- ☐ Acontece pois a corrente é maior que a corrente da carga;

$\square$  Quando a corrente zera, observa-se uma redução em  $V_{GS}$ ;

$\square$  Isto gera uma corrente adicional em  $\mathcal{C}_{GD}$  e uma terceira parte no transitório de descarga.

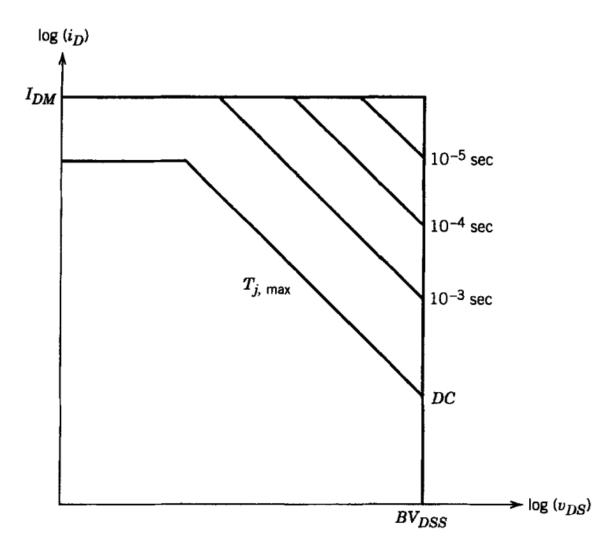

# Limites de operação

## Tensão máxima de bloqueio

$\square v_{GS,max} \rightarrow \text{associada a rigidez dielétrica do óxido};$

☐ Valor típico entre 20 e 30 V;

☐ Eletricidade estática pode causar a falha;

☐ Proteção com diodos Zener.

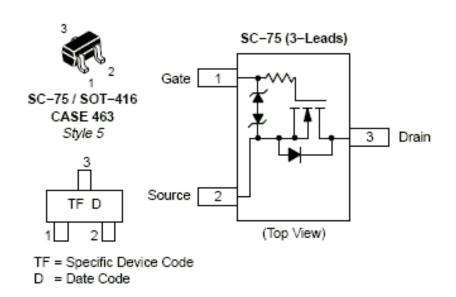

Fonte: On Semiconductors.

## Tensão máxima de bloqueio

$\square$   $BV_{DSS} \rightarrow$  tensão máxima de bloqueio sem que ocorra avalanche;

$\square$  Dopagem maior no corpo  $(p^+)$ ;

Papel importante da extensão da metalização do gate.

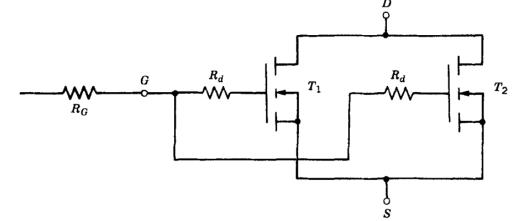

#### Conexão Paralela

- ☐ Simples de ser realizada;

- MOSFET: Dispositivo unipolar;

- Coeficiente de temperatura positivo (mobilidade cai co: a temperatura).;

- Gate não deve ser conectado em paralelo;

- Capacitância e indutâncias parasitas podem gerar oscilações.

- Layout de conexão simétrico!

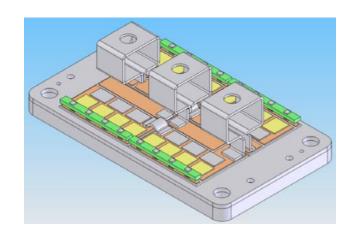

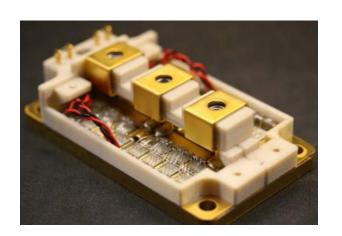

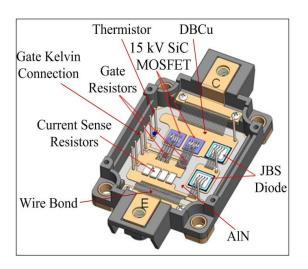

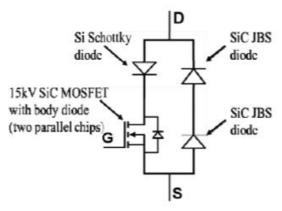

## Exemplo: Módulo MOSFET SiC – 1.2 kV e 400 A

Fonte: L. Boteler, D. Urciuoli, G. Ovrebo, D. Ibitayo and R. Green, "Thermal performance of a dual 1.2 kV, 400 a silicon-carbide MOSFET power module," 2010 26th Annual IEEE Semiconductor Thermal Measurement and Management Symposium

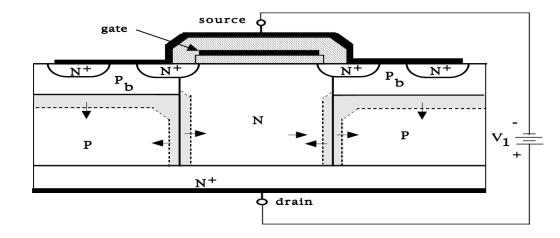

### TBJ Parasita

- ☐ Se a base for deixada flutuando, tem-se dois problemas:

- ightharpoonupRedução da tensão de bloqueio  $ightharpoonup BV_{CBO}$  para  $BV_{CEO}$ ;

- ➤ Latchup → Transistor entra em condução e não pode ser desligado;

- Mesmo que a base seja conectada a fonte, pode acontecer o acionamento se a derivada de  $v_{DS}$  for muito elevada durante o turn-off;

- Limita a taxa de variação de tensão do dispositivo.

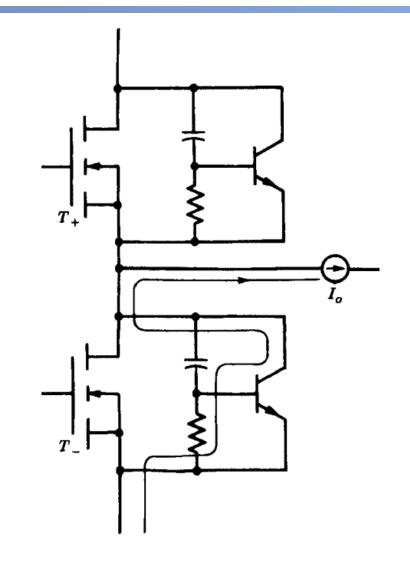

## TBJ Parasita - Circuito em meia ponte

- Quando  $T_+$  e  $T_-$  estão em bloqueio (tempo morto), o diodo de  $T_-$  conduz a corrente de saída;

- $\square$  Então  $T_+$  entra em condução e o diodo entra em recuperação reversa;

- $\square$  A corrente de recuperação reversa circula por  $C_{gd}$  de  $T_{-}$ ;

- ☐ Se a recuperação for abrupta, pode acionar o transistor;

- □ *T*\_ vai ser destruído visto que haverá um curtocircuito no barramento cc.

## TBJ Parasita - Circuito em meia ponte

- Solução: impedir a circulação de corrente pelo diodo de corpo;

- ☐ MOSFETs de silício modernos já são projetados sem essa abordagem;

- ☐ Isto é obtido por meio da otimização do projeto do diodo de corpo;

- Minimização da corrente de recuperação reversa e da resistência corpo-fonte.

# Área de operação segura

#### Obrigado pela Atenção

www.gesep.ufv.br

https://www.facebook.com/gesep

https://www.instagram.com/gesep\_vicosa/

https://www.youtube.com/channel/UCe9KOSGORXh hDBIcxMU2Nw

https://play.google.com/store/apps/details?id=br.developer.gesep.estimate

# Avanços e estruturas melhoradas

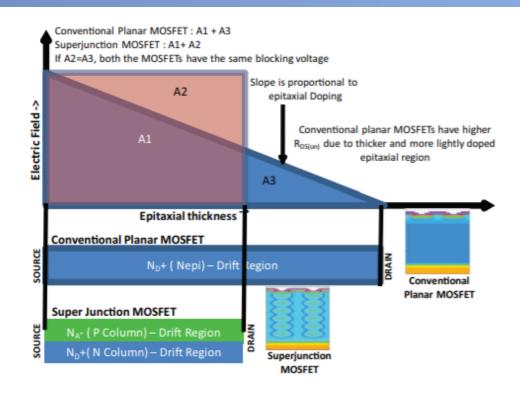

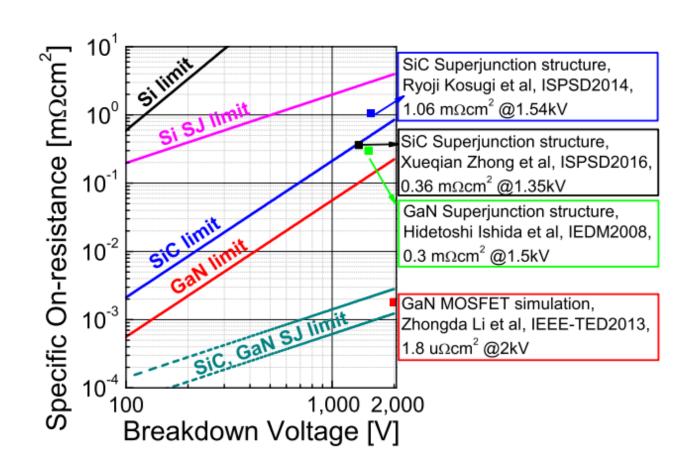

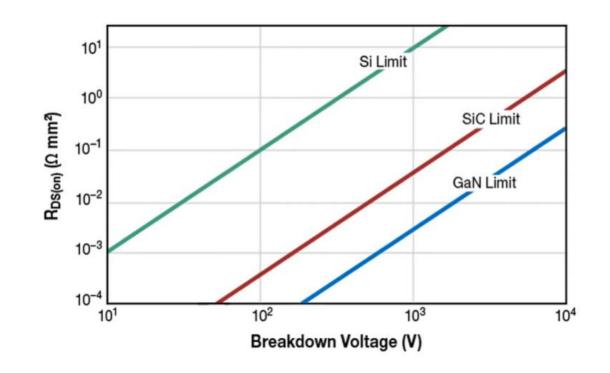

### Limites da estrutura planar

■ Não existe modulação de condutividade;

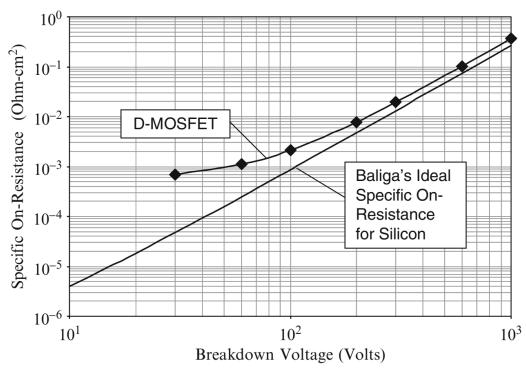

☐ Existirá um limite que vai relacionar a tensão de bloqueio e a resistência por unidade de área

$$R_{on-ideal} = \frac{4BV^2}{\varepsilon_S \mu_n E_C^3}$$

Fonte: B. Jayant Baliga. "Advanced Power MOSFET Concepts", Springer, 2010.

### Problema → altas tensões de bloqueio

- ☐ Existe um limite para a tecnologia;

- Novas estruturas são necessárias para extender os limites.

Fonte: Vishay Device Application Note AN849: Power MOSFET Basics Understanding Superjunction Technology .

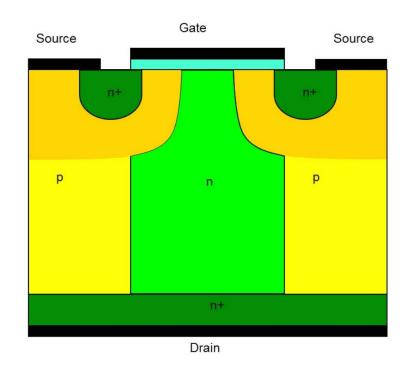

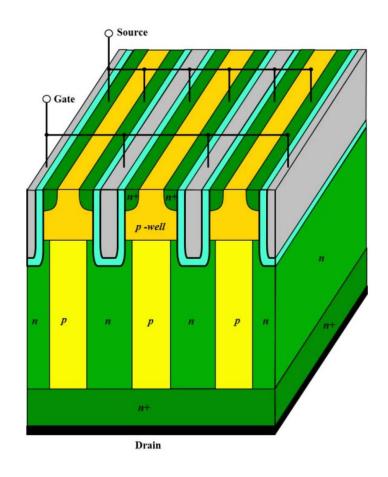

#### **MOSFET Planar versus MOSFET Trench**

- Trench: Menos espaço e consequentemente permite mais elementos em paralelo;

- Para a mesma área, consegue-se conduzir mais corrente;

- $\square$  Redução de  $R_{s,on}$ ;

- ☐ Dispositivo menor → menor capacitância → dispositivo mais rápido!

Fonte: F. Iannuzzo, C. Abbate and G. Busatto, "Instabilities in Silicon Power Devices: A Review of Failure Mechanisms in Modern Power Devices," in IEEE Industrial Electronics Magazine, vol. 8, no. 3, pp. 28-39, Sept. 2014, doi: 10.1109/MIE.2014.2305758.

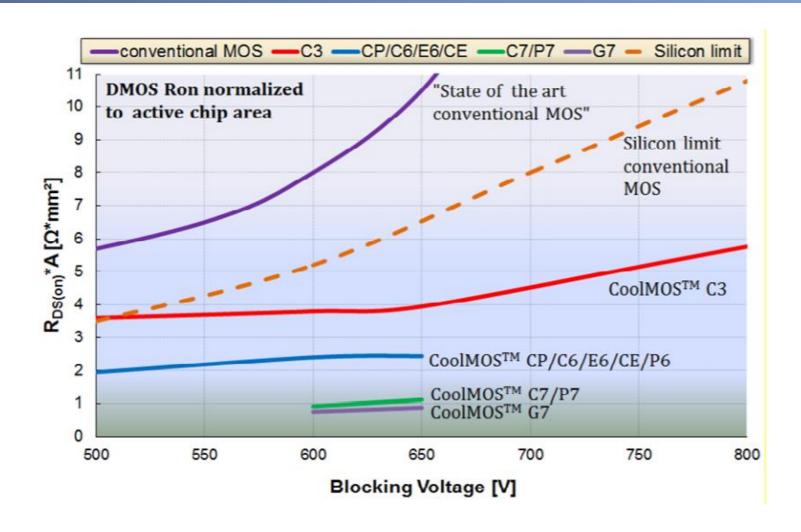

## SJ MOSFET

- Superjunção → Reportado em 1978;

- ☐ CoolMOS (Infineon) e MDMesh (ST microelectronics);

Fonte: F. Iannuzzo, C. Abbate and G. Busatto, "Instabilities in Silicon Power Devices: A Review of Failure Mechanisms in Modern Power Devices," in IEEE Industrial Electronics Magazine, vol. 8, no. 3, pp. 28-39, Sept. 2014, doi: 10.1109/MIE.2014.2305758.

### Princípio de funcionamento

- ☐ Camadas p e n com a mesma dopagem;

- ☐ Camada de depleção formada quando o dispositivo está reversamente polarizado;

- ☐ A distribuição de campo apresenta duas componentes;

- A distribuição de campo ao longo do comprimento do dispositivo torna-se retangular.

#### Princípio de funcionamento

- Distribuição de campo triangular: Tensão de bloqueio é afetado pela espessura e pela dopagem;

- Distribuição plana: pode-se mudar apenas o comprimento;

- □ SJ MOSFET: Apenas a espessura precisa ser mudada para bloquear mais tensão;

- ☐ Se o comprimento reduz, pode-se reduzir a área;

- ☐ Se o dispositivo é menor, menores capacitâncias!

Fonte: Vishay Device Application Note AN849: Power MOSFET Basics Understanding Superjunction Technology .

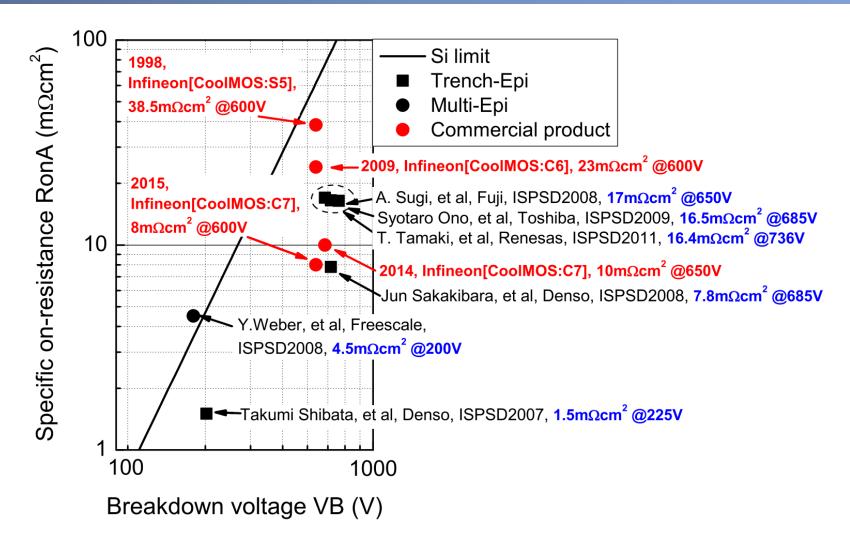

## SJ MOSFET

Fonte: F. Udrea, G. Deboy and T. Fujihira, "Superjunction Power Devices, History, Development, and Future Prospects," in IEEE Transactions on Electron Devices, vol. 64, no. 3, pp. 713-727, March 2017, doi: 10.1109/TED.2017.2658344.

## SJ MOSFET tipo Trench

Fonte: F. Udrea, G. Deboy and T. Fujihira, "Superjunction Power Devices, History, Development, and Future Prospects," in IEEE Transactions on Electron Devices, vol. 64, no. 3, pp. 713-727, March 2017, doi: 10.1109/TED.2017.2658344.

## SJ MOSFET

$Fonte: Infine on Technologies.\ AN\_201703\_PL52\_015\ 600\ V\ CoolMOS^{TM}\ P7\ Infine on `s\ most\ well\ balanced\ high\ voltage\ MOSFET\ technology\ .$

### Materiais de Banda Larga

| Parâmetro                                                 | Si              | GaAs                | 4H-SiC            | 6H-SiC            | 3C-SiC              | 2H-GaN              | Diamante            |

|-----------------------------------------------------------|-----------------|---------------------|-------------------|-------------------|---------------------|---------------------|---------------------|

| Energia de banda proibida, $E_g$ (eV)                     | 1,1             | 1,42                | 3,3               | 3,0               | 2,3                 | 3,4                 | 5,5                 |

| Campo elétrico crítico, $E_c$ (MV/cm)                     | 0,25            | 0,6                 | 2,2               | 3                 | 1,8                 | 3                   | 10                  |

| Velocidade de arraste<br>dos elétrons, <i>vsat</i> (cm/s) | $1 \times 10^7$ | $1,2 \times 10^{7}$ | $2 \times 10^{7}$ | $2 \times 10^{7}$ | $2,5 \times 10^{7}$ | $2,2 \times 10^{7}$ | $2,7 \times 10^{7}$ |

| Condutividade térmica, λ (W/cm-K)                         | 1,5             | 0,5                 | 4,9               | 4,9               | 4,9                 | 1,3                 | 22                  |

$$R_{on-ideal} = \frac{4BV^2}{\varepsilon_S \mu_n E_C^3}$$

#### Estruturas melhoradas já investigadas

☐ SiC Planar MOSFET;

☐ Trench SiC MOSFET;

☐ SJ SiC MOSFET.

Fonte: F. Udrea, G. Deboy and T. Fujihira, "Superjunction Power Devices, History, Development, and Future Prospects," in IEEE Transactions on Electron Devices, vol. 64, no. 3, pp. 713-727, March 2017, doi: 10.1109/TED.2017.2658344.

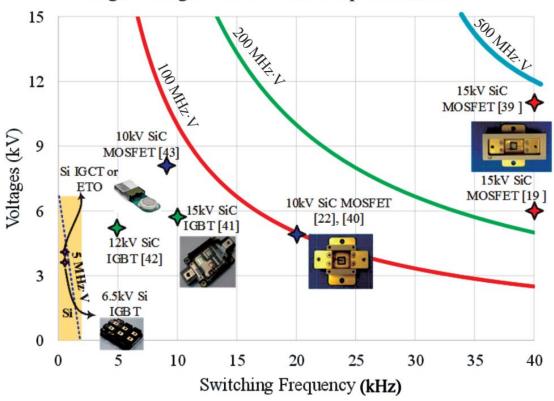

#### Estado da arte - dispositivos de alta tensão

#### High Voltage Power Devices Operation Area

Fontes: A. Q. Huang, Q. Zhu, L. Wang and L. Zhang, "15 kV SiC MOSFET: An enabling technology for medium voltage solid state transformers," in CPSS Transactions on Power Electronics and Applications, vol. 2, no. 2, pp. 118-130, 2017.

K. Vechalapu, A. Negi and S. Bhattacharya, "Comparative performance evaluation of series connected 15 kV SiC IGBT devices and 15 kV SiC MOSFET devices for MV power conversion systems," 2016 IEEE Energy Conversion Congress and Exposition (ECCE).

#### Limites dos materiais

☐ 30 anos para atingir os limites do Silício;

☐ SiC e GaN: Possibilidade de estender os limites;

- Desafios:

- Materiais com maior densidade de defeitos!

- Desafios relacionados ao encapsulamento;

- Instabilidades;

- Confiabilidade.

Fonte: Efficient Power Conversion EPC. "How to GaN?"

#### Obrigado pela Atenção

www.gesep.ufv.br

https://www.facebook.com/gesep

https://www.instagram.com/gesep\_vicosa/

https://www.youtube.com/channel/UCe9KOSGORXh hDBIcxMU2Nw

https://play.google.com/store/apps/details?id=br.developer.gesep.estimate